brain wrote:OK, I was finally able to debug the hardware last night and found the bug. I burned a new standard KERNAL image and tried ramcheck. Every test passes...

Nice!

max.prg still gives the wrong number,

That's strange. "All" that max.prg does is: moving the screen down to $0400, setting the BASIC start to $0601, and leaving BASIC end as is. Which *should* result in 31231 BYTES FREE, when the read out before was 28159 BYTES FREE (it simply adds the 3072 bytes of $0400..$0FFF to BASIC memory).

and not sure what detect.prg should do.

You'd "normally" see a pattern of white vertical stripes on black that change from full black, thin white stripes, thick white stripes, white and back again to black within roughly 1/4 second.

This is a pattern sequence that is assumed to be fetched by VIC in the $0400..$0FFF address range, remaining on the data bus due to parasitic capacitance, and then read on the following half-cycle by the CPU, by accessing "open" address space in BLK4. If at any point the CPU doesn't see the data the VIC fetched on the preceding half-cycle, the test is aborted.

On my VFLI modded VIC-20 it works as supposed as I did not change the memory access architecture besides some careful repurposing of UC4 and U13. All signals still go over the mainboard and through the bus buffers.

As

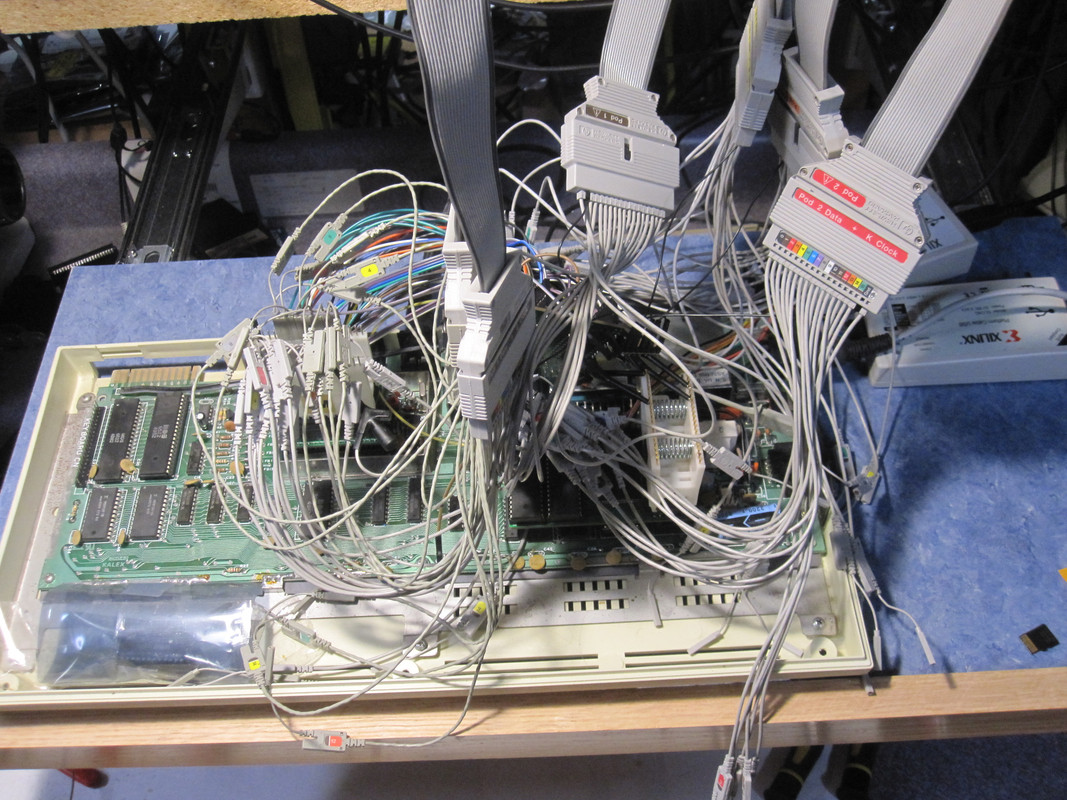

you've completely redesigned the VIC-20 mainboard in effect, with some extra barriers between VIC and CPU bus (and probably also reduced parasitic capacitance on the data bus signals - or even extra load because of the attached logic probes!) you get a false negative result. There's not much I can do here. Most important thing is - you get a display with the screen at $0400. That works, and that's great.

3k.prg does as the name suggests.

O.K.

Greetings,

Michael