Mike wrote: ↑Mon May 04, 2020 1:49 pm

Jim,

I think the fundamental misunderstanding on your side is, that VIC addresses on the VA bus somehow are translated to CPU addresses on the CA bus. The reverse is the case. VIC has its own 14 bit address space, and selects itself there (during PΘ2=1 or, equivalently on the VIC-20, during SΘ2=1) for its registers when there's an address of $10xx on the VA bus.

I am not sure I am misunderstanding, but I might be mis-communicating what my project is doing. I agree on the VIC, the CA bus is translated into the VA bus, not the other way around, but in my design, I have placed all the RAM and ROM on my main PCB, which is is separated from both the VA and CA busses. As a result, I have chosen to make the "MA" bus look like the map the CPU sees, and this means that I have to convert the VA bus to the BA bus (which is essentially the same as the CA bus in mapping for now). There is also the pins of the CPU, which we can call UA for now.

Seen from the CPU, the address bus buffers map all CPU accesses within $8000..$9FFF to $0000..$1FFF on the VA bus (which consequently shows the VIC registers at $90xx for the CPU), and *all* others (i.e. CPU address in $0000..$7FFF or $A000..$FFFF) to $2000..$3FFF on the VA bus! Now except where those CPU addresses with /BLK4 = 1 happen to be in $0000..$03FF and $1000..$1FFF, the '133 in conjunction with the data bus '245 blocks all these accesses, and neither are any of the internal RAMs or VIAs or VIC on the VA bus selected. This is the situation on a stock VIC-20.

Or, conversely, in my design, if VA wants to see $0000-$1fff of memory, it needs to be directed to $8000=$9fff in the MA memory map.

For the VFLI mod, I had to remove the 'blockade' of the data bus for $0400..$0FFF effected by the '133 by tying high the original /RAMx signals, with the intended side effect that it also silences external +3K RAM expansions.

Understood. I plan to continue to support RAM signals in my design, but optionally turn them off so one can use them with the VIC-I.

I still don't see any merit in allowing VIC access to a full 64K range - or giving it access to the expansion port even! - when the price to pay is that its registers need to be mapped to other places in CPU space. Exactly 0% of existing software (including the KERNAL) will be able to cope with this.

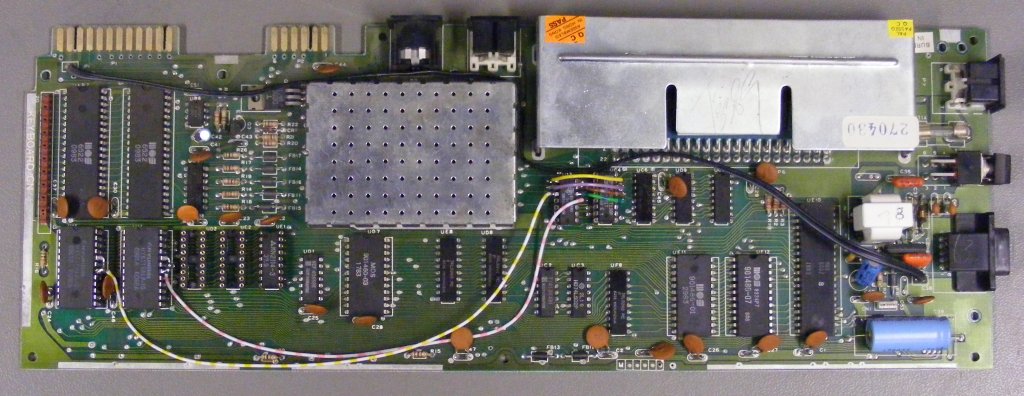

If I get my Verilog working correctly, they won't need to be. The initial goal of the project is to insert the PCBs, pull out all the RAM and ROM from the VIC-20, turn the unit on with stock KERNAL and BASIC, and the unit will function just as before (I know, boring... Why bother

). ONce I have that working, then I can work on the rest of my ideas.

Regards,

Michael

P.S. just in case this has somehow be missed: the 6502 does not tri-state its address bus during SΘ2=0. That's exactly the reason the '245 address bus buffers are there at all.

It's good information, though I am aware. In my design, the VA, CA, and my new 'MA' bus are isolated with the equivalent of '245s. The rules to connect them are:

- During s02 low, tie VA to MA and map VIC address requests to main memory read requests (it's a bit more complicated, since the memory bus is 8 bits and the VIC bus during this phase is 12 bits, but I will cover that later) VA13:12 = 0 -> $8xxx/1->$9xxx/2->0XXX/3->1xxx

- During s02 high and VIC-I access, tie UA to VA and convert va13

- During s02 high and any other IO access, map UA to CA

- During s02 high and RAM read access (for now), tie UA to MA

- for write, tie UA to MA AND CA, so data gets written to RAM on motherboard

Right now, I have a second CPLD that is doing the following:

- During so2 low, place VIC-I address on VIC-I socket address lines and place VIC-I socket data lines onto VIC-I data lines (output address, read data from main memory)

- During s02 high and IO address is in VIC register space, place address value from VIC-I socket onto VIC-I pins and connect VIC-I data pins to VIC-I socket data pins in the direction needed (R/W)

That all works. But, I need to swing the VIC-I from looking at it's own socket for address and data to my PCB. THat is where I am having troubles. I am sure it's Verilog coding error, just need to look at the data.

Jim